Bus I2C — affectation, dispositif, transfert de données, adressage

Lors de la création d'un circuit électronique, de nombreux développeurs sont confrontés à la nécessité d'utiliser un grand nombre de puces intermédiaires pour faire correspondre, échantillonner et adresser ses blocs individuels. Pour minimiser le nombre de puces auxiliaires, Philips a proposé une interface réseau série I2C bidirectionnelle dans les années 1980, conçue spécifiquement pour gérer plusieurs puces dans un seul appareil.

Aujourd'hui, Philips produit à elle seule plus d'une centaine de dispositifs compatibles I2C pour des équipements électroniques aux usages très variés : mémoire, systèmes de processeurs vidéo, convertisseurs analogique-numérique et numérique-analogique, pilotes d'affichage, etc.

Le bus I2C est une modification du protocole d'échange de données série capable de transmettre des données série 8 bits en mode "rapide" habituel à des débits de 100 à 400 kbps. Le processus d'échange de données est mis en oeuvre ici sur seulement deux fils (sans compter le fil commun) : ligne SDA pour les données et ligne SCL pour la synchronisation.

Le bus devient bidirectionnel du fait que les cascades de sorties des appareils connectés au bus ont des collecteurs ouverts ou des canaux, reproduisant ainsi le câblage ET. En conséquence, le bus minimise le nombre de connexions entre les puces, laissant moins de broches et de traces requises sur la carte. En conséquence, la carte elle-même s'avère plus simple, plus compacte et technologiquement plus avancée en production.

Ce protocole vous permet de désactiver les décodeurs d'adresses et d'autres logiques de négociation externes. Le nombre de puces pouvant fonctionner simultanément sur le bus I2C est limité par sa capacité — un maximum de 400 pF.

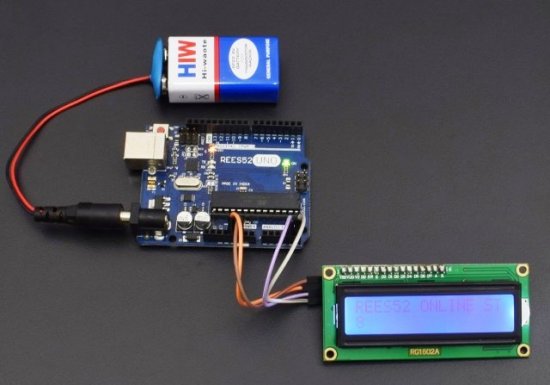

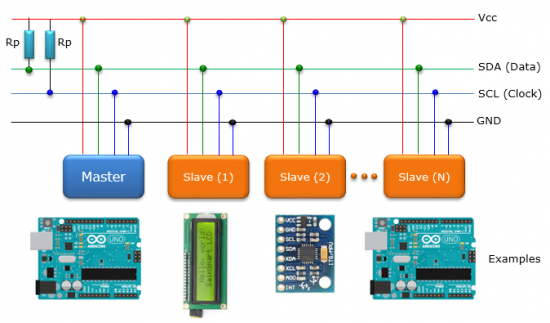

Les circuits intégrés compatibles I2C disposent d'un algorithme de suppression de bruit matériel pour garantir l'intégrité des données même en présence de fortes interférences. De tels dispositifs ont une interface qui permet aux microcircuits de communiquer entre eux même lorsque leurs tensions d'alimentation sont différentes. Dans la figure ci-dessous, vous pouvez vous familiariser avec le principe de connexion de plusieurs microcircuits via un bus commun.

Chacun des appareils connectés au bus a sa propre adresse unique, elle est déterminée par celle-ci et, selon l'objectif de l'appareil, il peut fonctionner comme récepteur ou comme émetteur. Lors de la transmission de données, ces appareils peuvent être maître (maître) ou esclave (esclave). Le maître est l'appareil qui initie le transfert de données et génère des signaux d'horloge sur la ligne SCL. L'esclave, par rapport au maître, est l'équipement destinataire.

A tout instant de fonctionnement sur le bus I2C, un seul appareil peut agir en tant que maître ; il génère un signal sur la ligne SCL.Un maître peut être soit un récepteur maître, soit un émetteur maître.

En principe, le bus autorise plusieurs maîtres différents, mais impose des restrictions sur les caractéristiques de formation des signaux de commande et de surveillance de l'état du bus ; cela signifie que plusieurs maîtres peuvent commencer à émettre en même temps, mais les conflits de ce genre sont éliminés grâce à l'arbitrage, c'est-à-dire le comportement du maître lorsqu'il détecte que le bus est occupé par un autre maître.

La synchronisation d'une paire d'appareils est assurée par le fait que tous les appareils sont connectés au bus, formant un câblage "ET". Initialement, les signaux SDA et SCL sont élevés.

DÉMARRER et ARRÊTER

L'échange démarre avec le maître générant l'état « START » : sur la ligne SDA, le signal passe de l'état haut à l'état bas, tandis que la ligne SCL a un niveau haut stable. Tous les appareils connectés au bus perçoivent cette situation comme une commande de démarrage de l'échange.

Chaque maître génère un signal d'horloge individuel sur la ligne SCL lors de la transmission de données sur le bus.

L'échange se termine par la formation de l'état STOP par le maître : sur la ligne SDA le signal passe de bas à haut, tandis que la ligne SCL a un niveau haut stable.

Le conducteur agit toujours comme source des signaux START et STOP. Dès que le signal « START » est fixe, cela signifie que la ligne est occupée. La ligne est libre lorsqu'un signal STOP est détecté.

Immédiatement après avoir déclaré l'état START, le maître commute la ligne SCL à l'état bas et envoie le bit le plus significatif du premier octet de message à la ligne SDA. Le nombre d'octets dans un message n'est pas limité.Les modifications sur la ligne SDA ne sont activées que lorsque le niveau du signal sur la ligne SCL est faible. Les données sont valides et ne doivent pas être modifiées uniquement lorsque l'impulsion de synchronisation est élevée.

L'accusé de réception que l'octet de l'émetteur maître a été reçu par le récepteur esclave est effectué en définissant un bit d'accusé de réception spécial sur la ligne SDA après la réception du huitième bit de données.

LA CONFIRMATION

Ainsi, l'envoi de 8 bits de données de l'émetteur au récepteur se termine par une impulsion supplémentaire sur la ligne SCL lorsque l'appareil récepteur passe au niveau bas sur la ligne SDA, indiquant qu'il a reçu l'octet entier.

La confirmation fait partie intégrante du processus de transfert de données. Le maître génère une impulsion de synchronisation. L'émetteur envoie un état bas au SDA pendant que l'horloge d'acquittement est active. Pendant que l'impulsion de synchronisation est élevée, le récepteur doit maintenir le SDA au niveau bas.

Si l'esclave de destination ne reconnaît pas son adresse, par exemple parce qu'il est actuellement occupé, la ligne de données doit être maintenue haute. Le maître peut alors donner un signal STOP pour interrompre la répartition.

Si la réception est effectuée par le récepteur maître, il est alors obligé d'informer l'émetteur esclave après la fin de la transmission - et non en confirmant le dernier octet. L'émetteur esclave libère la ligne de données afin que le maître puisse émettre un signal STOP ou un signal START répétitif.

La synchronisation des appareils est assurée par le fait que les connexions à la ligne SCL se font selon le principe "ET".

Le maître n'a pas le droit exclusif de contrôler la transition de la ligne SCL de bas en haut.Si l'esclave a besoin de plus de temps pour traiter un bit reçu, il peut indépendamment maintenir SCL bas jusqu'à ce qu'il soit prêt à recevoir le bit de données suivant. La ligne SCL dans une telle situation sera basse pendant la durée de la plus longue impulsion de synchronisation de bas niveau.

Les appareils avec le niveau bas soutenu le plus bas resteront inactifs jusqu'à la fin de la longue période. Lorsque tous les appareils ont terminé la période de synchronisation basse, SCL passe à l'état haut.

Tous les appareils commenceront à pointer haut et le premier appareil à terminer sa période sera le premier à régler la ligne SCL sur bas. En conséquence, la durée de l'état bas de SCL sera déterminée par l'état bas le plus long de l'impulsion de synchronisation de l'un des dispositifs, et la durée de l'état haut sera déterminée par la période de synchronisation la plus courte de l'un des dispositifs.

Les signaux de synchronisation peuvent être utilisés par les récepteurs comme moyen de contrôler la transmission des données au niveau des bits et des octets.

Si l'appareil est capable de recevoir des octets à un débit élevé, mais qu'il faut un certain temps pour stocker l'octet reçu ou se préparer à recevoir l'octet suivant, il peut continuer à maintenir SCL bas après avoir reçu et acquitté un octet, forçant le transmetteur en état de veille.

Un microcontrôleur sans circuits matériels intégrés, par exemple au niveau du bit, peut ralentir la vitesse d'horloge en augmentant la durée de leur état bas.En conséquence, le débit en bauds de l'appareil maître sera déterminé par la vitesse du appareil plus lent.

ADRESSER

Chaque appareil connecté au bus I2C possède une adresse de programme unique à laquelle le maître l'adresse en lui envoyant une commande spécifique. Les microcircuits du même type sont caractérisés par un sélecteur d'adresse, réalisé soit sous forme d'entrées numériques du sélecteur, soit sous forme analogique. Les adresses sont divisées dans l'espace d'adressage des appareils connectés au bus.

Le mode normal suppose un adressage sur sept bits. L'adressage fonctionne comme suit : après la commande « START », le maître envoie le premier octet, qui détermine quel appareil esclave doit communiquer avec le maître. Il existe également une adresse d'appel commune qui définit tous les appareils sur le bus, tous les appareils y répondent (théoriquement) par un acquittement, mais en pratique c'est rare.

Ainsi, les sept premiers bits du premier octet sont l'adresse de l'esclave. Le bit le moins significatif, le huitième, indique la direction d'envoi des données. S'il y a un « 0 », alors l'information sera écrite du maître vers cet esclave. Si « 1 », l'information sera lue par le maître depuis cet esclave.

Une fois que le maître a fini d'envoyer l'octet d'adresse, chaque esclave y compare son adresse. Toute personne ayant la même adresse est un esclave et est définie comme un émetteur esclave ou un récepteur esclave, en fonction de la valeur du bit le moins significatif de l'octet d'adresse.

Une adresse esclave peut comprendre des parties fixes et programmables. Très souvent, un grand nombre d'appareils du même type fonctionnent dans un système, alors la partie programmable de l'adresse permet l'utilisation d'un maximum d'appareils du même type sur le bus. Le nombre de bits programmables dans l'octet d'adresse dépend du nombre de broches libres sur la puce.

Parfois, une broche avec un réglage analogique de la plage d'adresses programmable est suffisante, par exemple le SAA1064 - un pilote d'indicateur LED qui a exactement une telle implémentation. Le potentiel d'une broche particulière détermine le décalage de l'espace d'adressage de la puce afin que les puces du même type n'entrent pas en conflit en fonctionnant sur le même bus. Toutes les puces prenant en charge le bus I2C contiennent un ensemble d'adresses que le fabricant spécifie dans la documentation.

La combinaison « 11110XX » est réservée à l'adressage 10 bits. Si nous imaginons l'échange de données de la commande « START » vers la commande « STOP », cela ressemblera à ceci :

Les formats d'échange de données simples et combinés sont autorisés ici. Le format combiné signifie qu'entre « START » et « STOP » le maître et l'esclave peuvent agir comme récepteurs et émetteurs, ce qui est utile par exemple dans la gestion de la mémoire série.

Laissez le premier octet de données transférer une adresse mémoire. Ensuite, en répétant la commande « START » et en lisant l'adresse de l'esclave, les données de la mémoire fonctionneront. Les décisions d'incrémenter ou de décrémenter automatiquement l'adresse précédemment accédée sont prises par le développeur du dispositif après avoir préalablement étudié la documentation de la puce. D'une manière ou d'une autre, après avoir reçu la commande START, tous les appareils doivent restaurer leur logique et se préparer au fait que l'adresse sera désormais nommée.